合創(chuàng)資本劉華瑞 聚焦數字集成電路設計領域的研發(fā)趨勢與投資邏輯

在半導體產業(yè)中,數字集成電路(Digital IC)作為信息處理與計算的核心,其設計研發(fā)的前沿動態(tài)與創(chuàng)新方向,一直是產業(yè)界與投資界關注的焦點。合創(chuàng)資本合伙人劉華瑞先生,憑借其深厚的產業(yè)背景與敏銳的投資洞察,對數字IC設計領域的研發(fā)趨勢有著獨到的見解。本文將結合劉華瑞的觀點,探討當前數字集成電路設計領域的關鍵研發(fā)關注點。

一、高性能計算與異構集成的核心驅動力

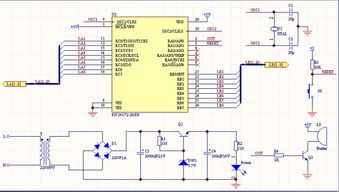

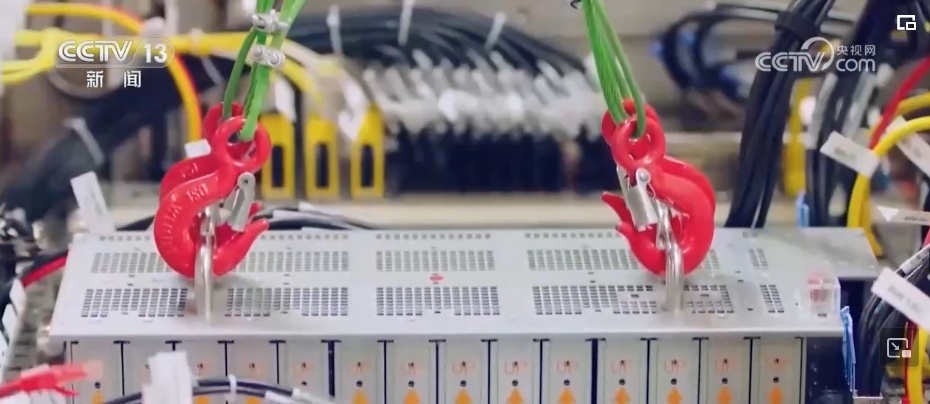

劉華瑞指出,隨著人工智能、大數據、云計算等應用的爆發(fā)式增長,市場對算力的需求呈指數級攀升。這直接驅動了數字IC設計向更高性能、更低功耗的方向演進。傳統(tǒng)的同構計算架構已逐漸遇到瓶頸,因此,異構計算與集成成為研發(fā)的核心路徑。這不僅僅是CPU、GPU、FPGA、ASIC等不同計算單元在系統(tǒng)級的組合,更深入到芯片級(Chiplet)甚至IP核級別的緊密集成與協同。研發(fā)重點在于如何通過先進的架構設計、互聯協議(如UCIe)、封裝技術(如2.5D/3D封裝)和軟件工具鏈,實現異構單元間的高效、低延遲、高帶寬通信與任務調度,從而最大化整體能效比。

二、先進工藝節(jié)點下的設計挑戰(zhàn)與協同優(yōu)化

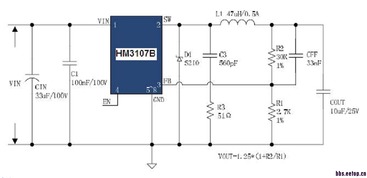

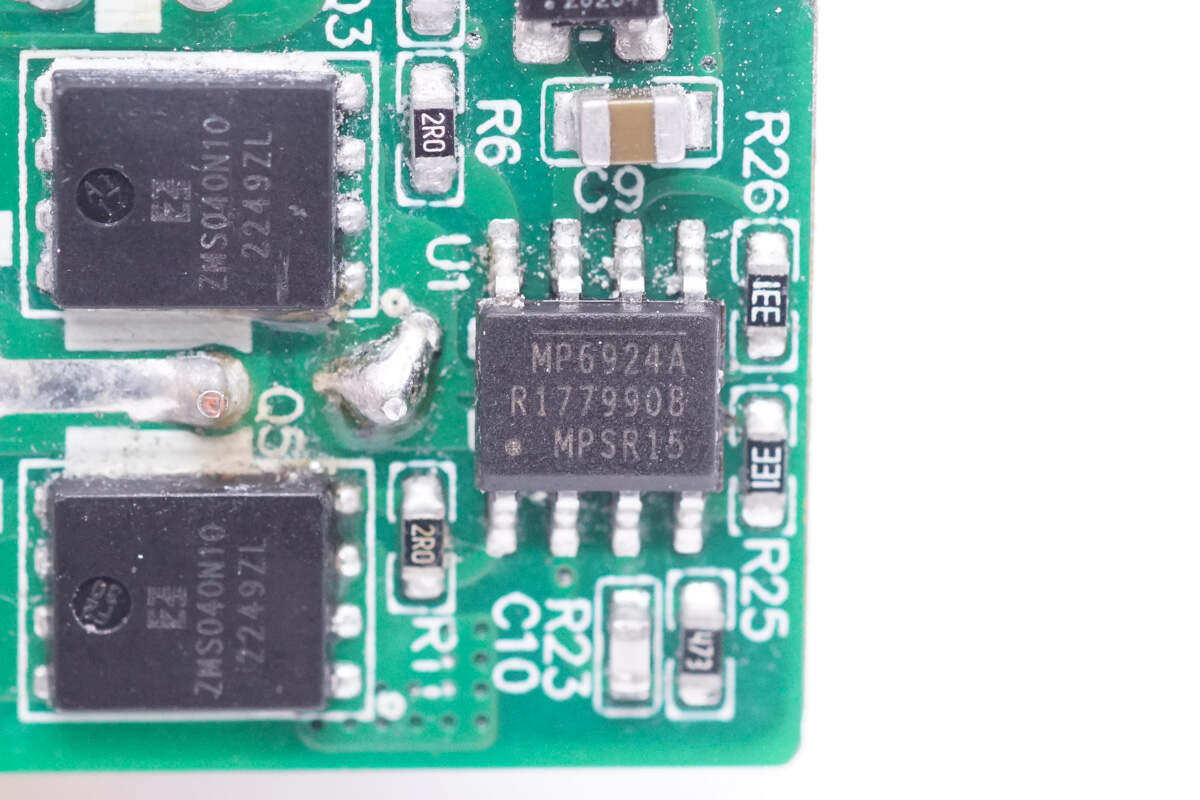

工藝制程的持續(xù)微縮(如向3nm、2nm及以下演進)在帶來性能提升和功耗降低的也引入了前所未有的設計挑戰(zhàn)。劉華瑞強調,研發(fā)的關注點已從單純追求工藝領先,轉向 “設計-工藝協同優(yōu)化”(DTCO) 和 “系統(tǒng)-技術協同優(yōu)化”(STCO) 。這要求設計團隊必須深入理解物理效應(如寄生效應、量子隧穿、工藝波動)、制造良率與可靠性問題,并在架構設計、電路設計、物理實現乃至EDA工具流程的各個環(huán)節(jié)進行精細化權衡與創(chuàng)新。例如,在標準單元庫設計、時鐘網絡架構、電源完整性、信號完整性以及熱管理等方面,都需要全新的設計方法論和工具支持。

三、從專用到可重構:靈活性與效率的平衡

面對快速變化的市場需求和應用場景的多樣化,劉華瑞觀察到,數字IC的研發(fā)正尋求在專用化(針對特定算法或任務進行極致優(yōu)化,如AI加速器、DPU)與靈活性之間找到最佳平衡點。因此,可重構計算架構成為重要研發(fā)方向。這類架構(如某些先進的FPGA、CGRA可重構陣列)能夠在硬件層面根據不同的計算任務進行動態(tài)配置,兼具ASIC的高能效和通用處理器的靈活性。其研發(fā)難點在于如何設計高效的可重構單元、互連網絡以及配套的編譯工具,以降低開發(fā)門檻并充分發(fā)揮硬件潛力。

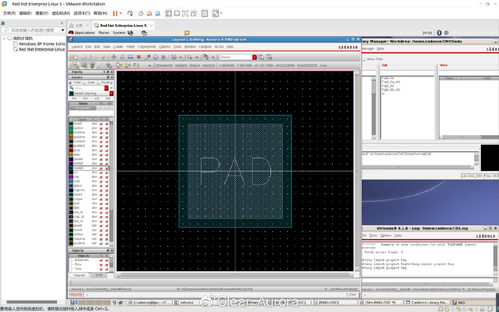

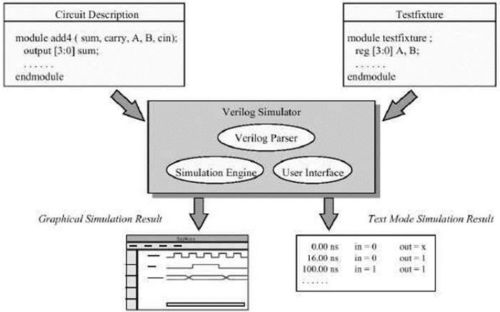

四、全流程EDA工具與設計方法學的創(chuàng)新

數字IC設計的高度復雜性使得EDA工具和設計方法學成為研發(fā)不可或缺的基石。劉華瑞認為,隨著系統(tǒng)復雜度和異構性的增加,傳統(tǒng)的設計流程正在被重塑。研發(fā)的關注點包括:

- 高層次綜合(HLS)與敏捷驗證:將設計抽象層次從RTL進一步提升,使用C/C++/SystemC等進行功能描述和快速原型驗證,以加速設計迭代。

- AI驅動的EDA工具:利用機器學習技術優(yōu)化布局布線、時序收斂、功耗分析等環(huán)節(jié),提升設計自動化水平和結果質量。

- 系統(tǒng)級設計與驗證平臺:構建包含硬件、軟件、甚至應用場景的虛擬原型,實現更早期的軟硬件協同設計與性能評估。

五、安全與可靠性的底層基石地位

在萬物互聯的時代,芯片的安全性(Security)和功能安全性(Functional Safety)已從附加屬性轉變?yōu)楸貍鋵傩浴⑷A瑞特別強調,在數字IC的研發(fā)初期就必須將安全架構納入核心考量。這涉及硬件安全模塊(如PUF、真隨機數發(fā)生器、加密引擎)、側信道攻擊防護、安全啟動、信任根建立以及面向汽車、工業(yè)等領域的高可靠性設計(如遵循ISO 26262、IEC 61508等標準)。這方面的研發(fā)需要從系統(tǒng)架構到電路實現的全面加固。

劉華瑞的觀點揭示,數字集成電路設計的研發(fā)前沿是一個多維度、多層次協同演進的生態(tài)系統(tǒng)。它不僅是晶體管與電路的創(chuàng)新,更是架構、算法、軟件、工藝、封裝乃至安全理念的深度融合。對于投資者和創(chuàng)業(yè)者而言,理解這些深層次的研發(fā)趨勢,把握其中在異構集成、設計方法學、能效平衡以及系統(tǒng)級安全等方面涌現出的創(chuàng)新機會,是在數字IC設計這一高技術壁壘、高價值賽道中取得成功的關鍵。未來的領先芯片,必將是那些在性能、能效、靈活性和可靠性上取得卓越平衡的系統(tǒng)級創(chuàng)新成果。

如若轉載,請注明出處:http://www.hbjjy.com.cn/product/40.html

更新時間:2026-04-28 11:34:35