通信集成電路芯片物理設計中的核心挑戰(zhàn)與創(chuàng)新解決方案

隨著5G、衛(wèi)星通信、高速以太網(wǎng)等技術的飛速發(fā)展,通信集成電路芯片正朝著更高頻率、更高帶寬、更低功耗和更大規(guī)模集成的方向演進。這給芯片的物理設計(Physical Design)環(huán)節(jié)帶來了前所未有的復雜性和一系列技術難點。物理設計是將電路邏輯網(wǎng)表轉化為可供制造的物理版圖的橋梁,其質量直接決定了芯片的最終性能、功耗、面積和可靠性。本文將深入剖析通信芯片物理設計中的主要難點,并探討相應的解決方案與研發(fā)趨勢。

一、 通信芯片物理設計的主要難點

- 高頻高速信號的完整性:通信芯片的核心在于信號的收發(fā)與處理。工作頻率從數(shù)GHz到數(shù)十GHz,甚至向太赫茲邁進,帶來了嚴重的信號完整性問題,包括:

- 時序收斂困難:高頻下時鐘抖動、時鐘偏差(Skew)對建立/保持時間的影響被放大,時序路徑的余量極小,收斂極其困難。

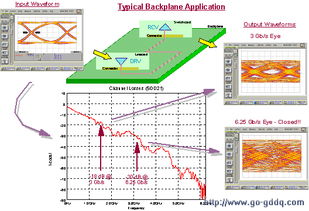

- 串擾與噪聲:密集布線中相鄰信號線之間的電容、電感耦合會導致信號串擾,破壞信號波形,引起誤碼。電源/地網(wǎng)絡的噪聲(IR Drop、地彈)也會嚴重影響高速模擬/射頻模塊和敏感數(shù)字電路的性能。

- 傳輸線效應:當信號波長與互連線長度可比擬時,互連線不再是理想導體,而需作為傳輸線處理,阻抗匹配、反射、損耗成為必須精細控制的問題。

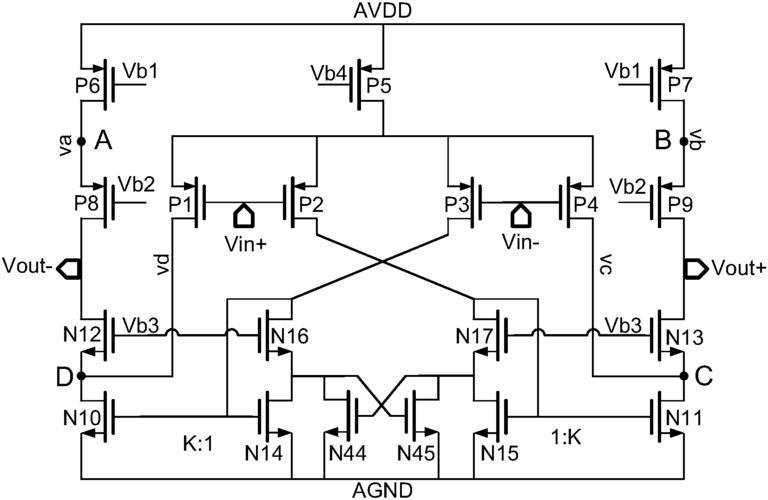

- 混合信號與射頻集成:現(xiàn)代通信芯片多為數(shù)模混合SoC,在同一顆芯片上集成了高性能的射頻前端、高速數(shù)據(jù)轉換器(ADC/DAC)、模擬鎖相環(huán)(PLL)以及大規(guī)模數(shù)字基帶處理器。難點在于:

- 噪聲隔離:數(shù)字電路的開關噪聲(通過襯底和電源網(wǎng)絡)極易干擾敏感的模擬和射頻電路,導致性能惡化(如相位噪聲增加、信噪比下降)。

- 版圖布局的協(xié)同優(yōu)化:模擬/射頻部分的版圖需要手工精心設計,講究對稱性、匹配性和寄生控制,而數(shù)字部分采用自動布局布線(APR),兩者在布局規(guī)劃、電源網(wǎng)絡、隔離結構上需要深度融合與協(xié)同設計。

- 功耗與熱管理的嚴峻挑戰(zhàn):為支持高速數(shù)據(jù)處理和傳輸,芯片功耗急劇上升。功耗難點體現(xiàn)在:

- 動態(tài)功耗與靜態(tài)功耗:高頻開關活動導致動態(tài)功耗巨大;采用先進工藝節(jié)點(如7nm、5nm)后,靜態(tài)漏電功耗占比顯著提升。

- 局部熱點:功率放大器(PA)、高速SerDes等模塊功耗密度極高,易形成局部熱點,影響器件壽命和電路可靠性,并可能引發(fā)熱致電遷移故障。

- 電源完整性:巨大的瞬態(tài)電流導致電源網(wǎng)絡出現(xiàn)顯著的IR Drop,使得晶體管實際驅動電壓不足,性能下降,嚴重時導致功能失效。

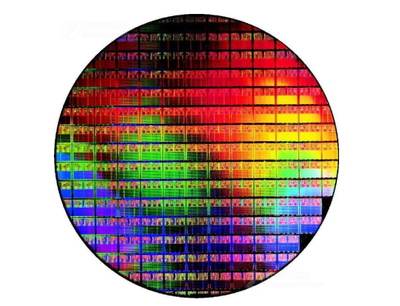

- 先進工藝節(jié)點的復雜性:為追求更高性能和集成度,通信芯片普遍采用16nm及以下的先進工藝,這引入了新的物理效應:

- 制造變異性與良率:光刻、化學機械拋光等工藝步驟的微小變異對器件和互連線特性的影響(如線邊緣粗糙度、厚度變化)更為顯著,直接影響電路性能和成品率。

- 設計規(guī)則激增:雙重 patterning/四重 patterning、FinFET器件結構等使得物理驗證(DRC/LVS)規(guī)則極其復雜,版圖設計約束增多。

- 寄生參數(shù)提取與建模:三維互連結構復雜,寄生電阻、電容、電感(RLCK)的精確提取和建模至關重要,但計算量巨大且準確性要求極高。

二、 針對難點的解決方案與研發(fā)方向

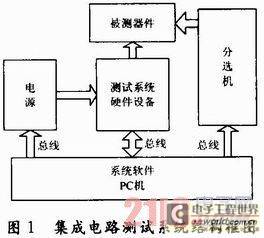

- 面向信號完整性的設計流程與工具:

- 簽核驅動的設計流程:在設計早期(如布局階段)就引入基于簽核精度的分析(如靜態(tài)時序分析STA、電源完整性分析),進行預測和優(yōu)化,而非僅在最后階段驗證。

- 協(xié)同設計與分析:將電磁場仿真、傳輸線分析、電源噪聲分析與傳統(tǒng)的布局布線工具深度集成,實現(xiàn)布線前、布線中、布線后的實時評估與優(yōu)化。例如,采用屏蔽線、差分對布線、自動阻抗控制布線等技術。

- 先進的時序收斂方法:運用片上偏差(OCV)高級建模、時鐘樹綜合(CTS)與時鐘網(wǎng)格(Clock Mesh)混合結構、有用的時鐘偏差(Useful Skew)等技術來應對高頻時序挑戰(zhàn)。

- 混合信號隔離與協(xié)同設計技術:

- 物理隔離策略:采用深N阱(DNW)、保護環(huán)(Guard Ring)、隔離溝槽、獨立電源域和地平面,從物理上阻斷噪聲耦合路徑。

- 規(guī)劃驅動的混合信號布局:在頂層規(guī)劃階段就為模擬/射頻模塊劃分專屬區(qū)域,預留足夠的隔離空間,并規(guī)劃全局的電源分配網(wǎng)絡(PDN),確保數(shù)字和模擬電源/地分離且低噪聲。

- 統(tǒng)一的設計環(huán)境:研發(fā)支持數(shù)字、模擬、射頻統(tǒng)一數(shù)據(jù)模型和設計流程的EDA平臺,實現(xiàn)跨域約束傳遞和聯(lián)合仿真。

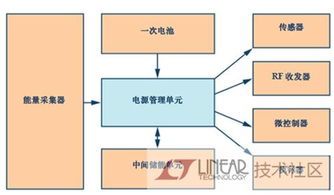

- 多維度功耗與熱完整性優(yōu)化:

- 系統(tǒng)級與架構級低功耗設計:采用動態(tài)電壓頻率縮放(DVFS)、電源門控(Power Gating)、多閾值電壓(Multi-Vt)庫、時鐘門控(Clock Gating)等技術。

- 精細化電源網(wǎng)絡設計與分析:使用高密度去耦電容(Decap)、片上穩(wěn)壓器、網(wǎng)格狀電源地網(wǎng)絡,并運用基于機器學習的IR Drop熱點預測工具進行早期優(yōu)化。

- 熱感知布局與封裝協(xié)同設計:在布局時考慮功耗分布,將高功耗模塊分散或靠近散熱通道;采用先進封裝技術(如硅中介層、3D IC)增強散熱能力,并進行芯片-封裝-系統(tǒng)(CPS)級熱仿真。

- 應對先進工藝的設計方法學創(chuàng)新:

- 設計-工藝協(xié)同優(yōu)化(DTCO):在設計階段就考慮工藝限制和變異,通過版圖風格(Layout Style)優(yōu)化、使用標準單元增強技術(如采用多高度單元、利用布線資源)來提升性能和良率。

- 機器學習輔助設計:利用機器學習模型預測布線擁塞、時序、功耗和良率,加速設計空間探索,自動優(yōu)化布局布線策略,甚至自動生成部分模擬模塊的版圖。

- 高精度物理驗證與仿真:采用基于場求解器的3D寄生參數(shù)提取工具,以及能夠處理復雜設計規(guī)則的增量式物理驗證引擎,確保設計的可制造性。

三、 結論

通信集成電路芯片的物理設計是一項涉及電路、器件、工藝、封裝、EDA工具等多學科的復雜系統(tǒng)工程。其核心難點圍繞著高頻、混合信號、低功耗和先進工藝四大主題展開。解決這些難題沒有單一的“銀彈”,而需要一整套從設計方法學、EDA工具鏈到跨領域協(xié)同創(chuàng)新的綜合解決方案。隨著6G、太赫茲通信等前沿技術的發(fā)展,物理設計將面臨更極端的頻率、更異構的集成和更嚴苛的能效要求。研發(fā)的重點將繼續(xù)向更智能(AI/ML驅動)、更協(xié)同(芯片-封裝-系統(tǒng)一體化)、更精準(量子級效應建模)的方向演進,以支撐下一代通信系統(tǒng)的芯片實現(xiàn)。

如若轉載,請注明出處:http://www.hbjjy.com.cn/product/73.html

更新時間:2026-04-28 07:26:14