數字集成電路的分類與特點解析 從設計到研發的視角

數字集成電路是構成現代信息社會的基石,從智能手機到數據中心,其身影無處不在。其研發過程高度復雜且分工明確,而不同類型的數字電路在設計與應用上各有千秋。本文將從研發的視角,系統解析數字集成電路的主要分類及其核心特點。

一、 按集成度分類:規模決定復雜度

這是最基礎、最直觀的分類方式,直接反映了芯片的工藝水平和設計能力。

- 小規模集成電路(SSI):包含邏輯門數量通常在10個以下,如基本的與門、或門、非門等。

- 特點:結構簡單,功能單一,常用于教學、原型驗證或作為更大系統中的基礎構件。

- 研發側重:在先進工藝節點下,單獨研發SSI已不常見,其設計更多作為標準單元庫的一部分,由晶圓廠或IP公司提供。

- 中規模集成電路(MSI):包含邏輯門數量在10至100個之間,如編碼器、譯碼器、計數器、寄存器等。

- 特點:實現了特定的邏輯功能模塊,是構建復雜系統的“積木塊”。

- 研發側重:通常作為標準IP(知識產權核)進行設計和驗證,強調功能的正確性、時序的穩定性和接口的標準化,以便在不同項目中復用。

- 大規模集成電路(LSI):包含邏輯門數量在100至10,000個之間,如早期的微處理器、存儲器芯片、簡單微控制器等。

- 特點:可完成一個子系統或一個完整的功能,如8位CPU。

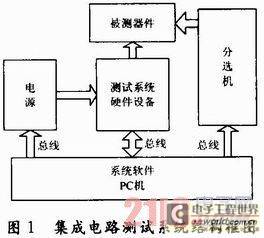

- 研發側重:開始涉及系統架構設計、模塊劃分、片上總線設計等。研發流程需要完整的數字前端(RTL設計、驗證)和后端(物理設計)團隊協作。

- 超大規模集成電路(VLSI):包含邏輯門數量在10,000至1,000,000個之間,是現代芯片的主流,如復雜的微處理器、DSP、SoC中的主要模塊。

- 特點:集成度極高,性能強大,設計復雜。

- 研發側重:高度依賴電子設計自動化(EDA)工具。研發核心挑戰包括時序收斂、功耗管理(動態與靜態)、信號完整性、可測試性設計(DFT)以及巨大的驗證工作量。團隊需要精通特定領域(如CPU、GPU、AI加速器)的架構師。

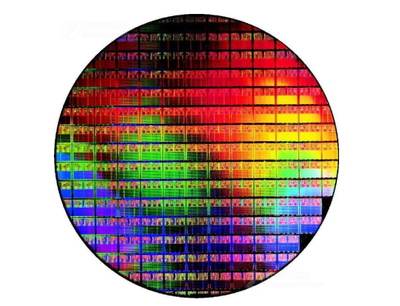

- 特大規模集成電路(ULSI)和巨大規模集成電路(GSI):門數量超過百萬甚至數十億,代表最先進的工藝水平,如多核CPU、高端GPU、大型SoC。

- 特點:采用納米級工藝,集成了處理器、存儲器、接口、模擬模塊等,形成一個完整的片上系統。

- 研發側重:研發是一項龐大的系統工程。特點包括:

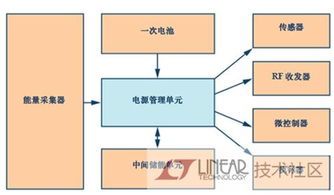

- 異構集成:整合不同架構的計算單元(CPU/GPU/NPU)。

- 軟硬件協同設計:芯片設計與系統軟件、驅動、編譯器同步進行。

- 先進封裝:可能采用2.5D/3D封裝技術以繼續提升性能、降低功耗。

- 高昂的成本與風險:研發投入動輒數億美元,對團隊技術、管理和資金都是極限考驗。

二、 按電路結構分類:架構決定應用

此分類決定了芯片的執行模式和工作原理。

- 通用型集成電路:

- 代表:微處理器(MPU)、微控制器(MCU)、數字信號處理器(DSP)。

- 特點:通過執行存儲的程序(軟件)來完成多樣化的任務,靈活性極高。

- 研發特點:研發聚焦于提升核心的通用計算性能(IPC、主頻)、能效比、指令集擴展(如向量、AI指令),以及構建豐富的外設生態。

- 專用集成電路:

- 代表:專用標準產品(ASSP),如手機基帶芯片、音視頻編解碼芯片。

- 特點:為特定應用或市場設計,功能固定,在特定任務上性能和能效通常優于通用芯片。

- 研發特點:深度定制化設計,算法硬件化是關鍵。研發團隊需與算法團隊緊密合作,進行硬件/軟件劃分,用專用硬件電路(如流水線、并行處理單元)實現關鍵算法,以追求極致的吞吐量和能效。

- 可編程邏輯器件:

- 代表:現場可編程門陣列(FPGA)、復雜可編程邏輯器件(CPLD)。

- 特點:硬件功能可由用戶通過編程(燒寫配置文件)來定義,提供了硬件靈活性與高性能的折中方案。

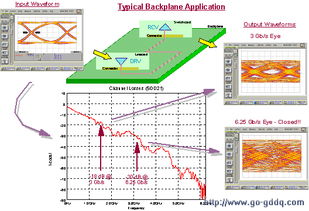

- 研發特點(指FPGA芯片本身的研發):研發重點在于設計可編程的布線資源、邏輯單元(CLB)、嵌入式硬核(如SerDes、DDR控制器)和豐富的IP庫。其挑戰在于如何在提供靈活性的盡量減少由此帶來的面積、功耗和速度上的開銷。

三、 按制造工藝分類:工藝奠定基石

工藝是芯片物理實現的載體,直接影響性能、功耗和成本。

- CMOS工藝:當今絕對的主流。

- 特點:靜態功耗極低(僅漏電功耗),集成度高,抗干擾能力強,已成為數字IC的標準工藝。

- 研發影響:幾乎所有數字芯片研發都基于CMOS工藝庫。研發人員必須深刻理解工藝節點(如7nm、5nm)帶來的物理效應(短溝道效應、遷移率變化等),并利用工藝提供的特殊器件(如FinFET)進行設計。

- 雙極型工藝(如TTL、ECL):曾經的主流,現多用于特殊領域。

- 特點:速度快,驅動能力強,但功耗大,集成度低。

- 研發影響:在現代超高速(如微波、光纖通信)或高驅動需求的部分模擬/混合信號電路中仍有應用。相關研發需要專業的模擬/射頻設計知識。

研發視角下的:

數字集成電路的分類并非孤立,而是交織在一起,共同定義了一款芯片的“身份”。在研發實踐中,選擇何種類型的芯片進行開發,取決于目標市場、性能需求、功耗預算、研發周期和成本約束。例如,研發一款AIoT設備的主控芯片,可能選擇基于成熟CMOS工藝,集成一個MCU核心、專用AI加速模塊和多種接口的SoC(屬于VLSI/ULSI范疇的ASSP)。整個過程需要系統架構師、數字設計工程師、驗證工程師、物理設計工程師和軟件工程師的緊密協作,穿越從行為級描述到GDSII版圖的完整研發流程,最終將抽象的算法和邏輯,轉化為實實在在的硅芯片。理解這些分類與特點,是成功進行數字IC研發的第一步。

如若轉載,請注明出處:http://www.hbjjy.com.cn/product/79.html

更新時間:2026-04-28 08:25:12